## **FEATURES**

#### General

- Highly flexible, high-performance synchronous sampled-amplitude read/write channel

- High-performance channel data rates with support up to 72 MHz

- Support for 1- and 2-bit NRZ interfaces

## Sequence Detection

- Rate 2/3 RLL (1, 7) ENDEC

- Complete implementation of synchronous channel with only two off-chip nonprecision passive components

- VGA with digital gain control

- Seventh-order Equi-ripple phase filter with variable cutoff and variable boost using two symmetrical real-axis zeros

- SofTarget<sup>™</sup> PRML sequence detection

- Digital timing recovery and offset control

#### Error Tolerance

- Error-tolerant synchronization mark detection

- Channel-quality circuitry for statistical performance-related feedback of the channel

- Erasure-pointer generation

#### **Head Support**

Supports monolithic, composite, thin-film, MIG, and magneto-resistive heads

#### Technology

■ 100-pin Very Tight Pitch Quad Flat Pack (VQFP); low-power CMOS technology

# Sampled-Amplitude Digital R/W Channel Device

#### **OVERVIEW**

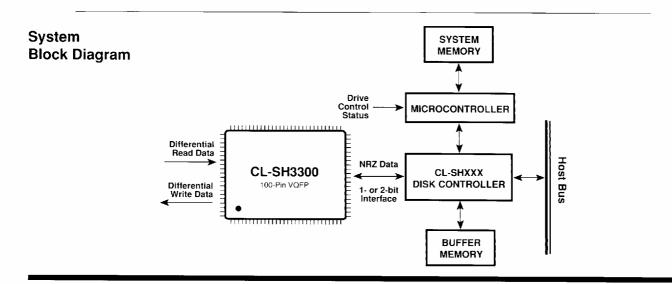

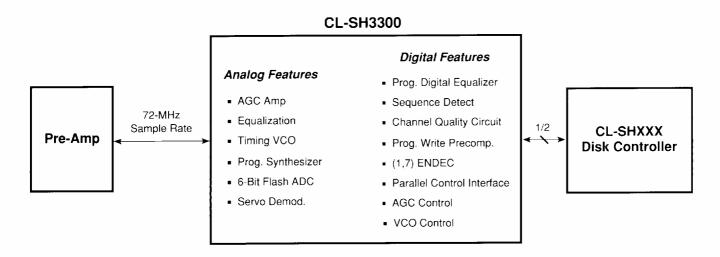

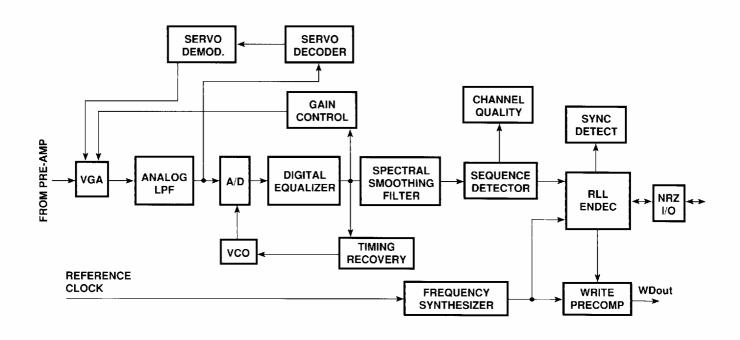

The CL-SH3300 Sampled-Amplitude Digital Channel is a VLSI component designed to work with a disk controller and pre-amp to provide the majority of drive and controller hardware necessary to build a state-of-the-art, high-density magnetic disk drive data path. The CL-SH3300 implements a sampled-amplitude read/write channel employing advanced partial-response polynomials and sequence detection technology. It supports user data rates up to 48 Mbits per second and channel rates up to 72 MHz. Additionally, a 3.3-volt version of the CL-SH3300 will be offered as the CL-SH3303.

The CL-SH3300 includes many features that allow the disk drive designer to include auto-calibration strategies in the channel design. A channel-quality circuit will interpret the characteristics of the incoming transitions and give the drive firmware feedback that can then be used to tune the channel for better results. Additionally, the digital nature of the channel allows the disk drive designer to tailor the channel

(cont. next page)

# **OVERVIEW** (cont.)

parameters via programmable registers, resulting in a major reduction of passive components.

The CL-SH3300 offers digitally controlled loops to control gain, timing, and channel offset. Furthermore, the loops can be configured with control coefficients for both acquisition and tracking; the loops will reconfigure with the correct coefficients under control of the acquisition and tracking modes.

The CL-SH3300 also includes an analog servo gain stage to provide demodulation of recovered servo burst information.

The CL-SH3300 is a mixed-signal CMOS integrated circuit that implements a highly flexible synchronous channel. Partial response schemes such as PR4 and EPR4 may be implemented, and the SofTarget ™

Sequence detector provides a user-specific partial response scheme that allows the detection strategy to be customized for a specific pulse shape.

Additionally, the degree of flexibility in the CL-SH3300 architecture allows for more precise matching of HDA and channel electronics.

The CL-SH3300 offers a wide array of Power-down Modes, allowing the disk drive designer to achieve extremely low average power consumption.

The SofTarget technology, together with an on-chip filter specifically designed to minimize pole-tip effects or secondary gap effects, make the CL-SH3300 compatible with monolithic, composite, thin film, MIG and magneto-resistive heads.

CL-SH3300 Channel

# FUNCTIONAL BLOCK DIAGRAM

#### **ADVANTAGES**

## Key Features

- SofTarget™ Sequence Detector

- Error-tolerant synchronization

- Programmable equalization, sampling and detection alternatives

- Rate 2/3 RLL (1,7) Recording Code

- Intelligent Power Management

## Benefits

Flexible architecture supporting a broad range of partial-response polynomials. SofTarget allows the disk drive designer to tailor the behavior of the channel to a particular head/disk characteristic, thereby optimizing areal density.

Supports the higher soft error rates and higher defect densities encountered at higher recording densities.

Provide optimum match to channel characteristics and permit channel optimization.

Reduces nonlinear effects associated with closelyspaced transitions.

Minimizes operational and idle power consumption.